當(dāng)高頻晶體振蕩器信號(hào)彼此接近時(shí),另外,串?dāng)_很可能會(huì)影響抖動(dòng)每個(gè)輸出的性能.了解如何放置輸出時(shí)鐘Si538x/4石英晶體振蕩器上的引腳可實(shí)現(xiàn)最佳抖動(dòng)和串?dāng)_性能.本應(yīng)用筆記提供了Clock Builder Pro的“時(shí)鐘放置向?qū)?rdquo;概述以及如何使用它來(lái)為您的頻率計(jì)劃和設(shè)備配置獲得最佳的抖動(dòng)和串?dāng)_性能.

1.晶體振蕩器最低抖動(dòng)和串?dāng)_的設(shè)計(jì)準(zhǔn)則

在介紹“時(shí)鐘晶體振蕩器放置向?qū)?rdquo;如何工作以及如何使用它來(lái)實(shí)現(xiàn)特定有源晶體振蕩器的最低抖動(dòng)和串?dāng)_之前,Si538x/4x頻率計(jì)劃,請(qǐng)考慮以下輸出時(shí)鐘引腳配置準(zhǔn)則.

1.1盡可能使用差分輸出格式

為了獲得最佳性能,強(qiáng)烈建議使用差分輸出格式,例如LVDS,LVPECL,CML或HCSL.雖然晶體振蕩器放置向?qū)Р粫?huì)強(qiáng)制用戶選擇輸出格式,建議使用差分輸出,因?yàn)檫@些擺幅較低信令格式具有固有的平衡性,因此可以最大程度地減少共模噪聲的產(chǎn)生.共模噪聲通常是降低抖動(dòng)性能和串?dāng)_的關(guān)鍵因素.相反CMOS輸出振蕩器是單端,擺幅軌到軌和具有亞皮秒的邊緣速率.由于這些因素,CMOS輸出振蕩器會(huì)在以下情況下產(chǎn)生明顯的單端電流浪涌:所有時(shí)鐘晶體振蕩器,因此會(huì)產(chǎn)生很大的串?dāng)_.由于這些原因,應(yīng)在任何時(shí)候避免使用CMOS輸出尋求低抖動(dòng)性能時(shí)可能實(shí)現(xiàn).如果必須在頻率計(jì)劃中使用CMOS輸出,則最好放置此輸出盡可能遠(yuǎn)離其他時(shí)鐘,中間使用未使用的輸出.輸出格式可以輕松地在Clock Builder Pro配置向?qū)?/span>.

1.2小心放置時(shí)鐘銷(xiāo)

Clock Placement Wizard(時(shí)鐘晶體振蕩器放置向?qū)В⒎治鏊芯w振蕩器輸出,并安排它們,以避免放置會(huì)引起抖動(dòng)的晶振,集成帶寬彼此相鄰.常用的集成帶寬是12kHz至20MHz. ClockPlacement向?qū)г谄渌惴ㄖ惺褂么藥?/span>.如果兩個(gè)有源晶振,晶體振蕩器輸出之間的間隔接近20MHz輸出頻率,這可能會(huì)導(dǎo)致串?dāng)_問(wèn)題.

例如,如果振蕩器2為155.52MHz,振蕩器3為156.25MHz,則156.25MHz–155.52MHz=730kHz.由于730kHz在12kHz至20MHz的集成帶寬內(nèi),因此CPW的自動(dòng)放置算法假設(shè)有更好的選擇,我們嘗試找到一種避免將這兩個(gè)振蕩器相互放置的方法.這兩個(gè)輸出信號(hào)將如果并排放置,則會(huì)在730kHz和730kHz的倍數(shù)處產(chǎn)生雜散,這些雜散將在12kHz至20MHz的積分頻帶內(nèi).這些雜散會(huì)導(dǎo)致更高的抖動(dòng).如果有未使用的時(shí)鐘輸出,最好在兩個(gè)晶體振蕩器之間有一個(gè)未使用的時(shí)鐘輸出在此示例中,晶振2和晶振3.此外,晶振2和晶振3應(yīng)該與其他更高頻率放置在更遠(yuǎn)的地方它們之間的差距要大得多,并且超出了集成范圍.

請(qǐng)注意,積分帶寬接近度放置算法不適用于彼此簡(jiǎn)單整數(shù)倍的晶體振蕩器.例如,即使10MHzx2=20MHz和20MHz,也可以將20MHz振蕩器和10MHz振蕩器彼此并排放置.MHz–10MHz=10MHz,兩者都位于積分頻帶內(nèi).簡(jiǎn)單整數(shù)關(guān)系不是問(wèn)題的原因這是因?yàn)橐粋€(gè)時(shí)鐘的邊沿不相對(duì)于另一時(shí)鐘的邊沿移動(dòng).時(shí)鐘放置向?qū)⑷靠紤]在內(nèi).

1.3考慮降低輸出擺幅和I/O電壓

如果使用時(shí)鐘晶體振蕩器放置向?qū)o(wú)法獲得最佳性能,并且您的設(shè)計(jì)中包含了AN862手動(dòng)引腳放置的詳細(xì)信息,則可以通過(guò)使用較低的I/O電壓(2.5或1.8V)來(lái)改善差分晶振,晶體振蕩器抖動(dòng)性能.用于CMOS和/或定制的低擺幅差分輸出信號(hào)設(shè)置.

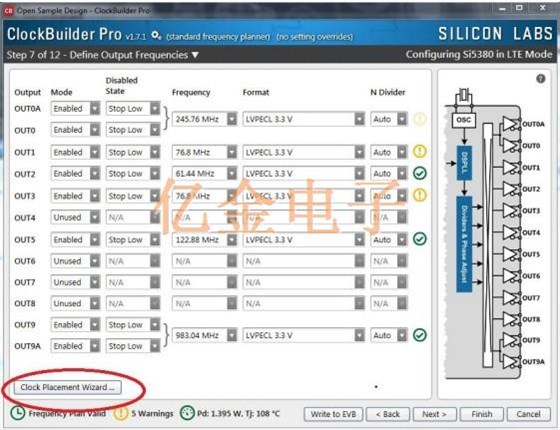

2.使用時(shí)鐘晶體振蕩器放置向?qū)г?ldquo;定義輸出頻率”菜單步驟中訪問(wèn)“時(shí)鐘放置向?qū)?rdquo;,如下所示.請(qǐng)注意,此示例頻率計(jì)劃的某些輸出旁邊當(dāng)前有警告符號(hào).這些警告表明輸出位置尚未針對(duì)抖動(dòng)和串?dāng)_進(jìn)行優(yōu)化.

圖2.1.定義的輸出頻率,訪問(wèn)時(shí)鐘晶體振蕩器放置向?qū)?/span>

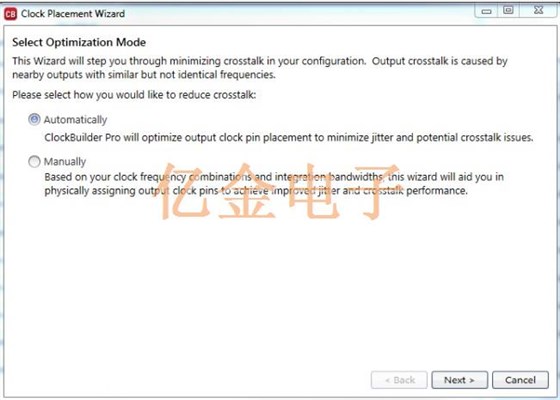

單擊“時(shí)鐘放置向?qū)?rdquo;按鈕,出現(xiàn)兩個(gè)選項(xiàng):

1.自動(dòng)優(yōu)化輸出時(shí)鐘放置,以運(yùn)行自動(dòng)放置算法.

2.手動(dòng)優(yōu)化輸出時(shí)鐘位置,從而可以快速重新排列輸出順序.

圖2.2.選擇時(shí)鐘晶體振蕩器放置的優(yōu)化模式

3.結(jié)論

通過(guò)遵循本應(yīng)用筆記中描述的準(zhǔn)則,并使用時(shí)鐘晶體振蕩器放置向?qū)?/span>,可以快速輕松地實(shí)現(xiàn)Si534x/8x系列抖動(dòng)振蕩器和時(shí)鐘晶體振蕩器的最佳抖動(dòng)和串?dāng)_性能.

SMI晶振,86M0368 -16,86SMX進(jìn)口晶振,6G相關(guān)設(shè)備晶振

SMI晶振,86M0368 -16,86SMX進(jìn)口晶振,6G相關(guān)設(shè)備晶振 日本SMI晶體,53SMX石英晶振,53M320-16,6G基站晶振

日本SMI晶體,53SMX石英晶振,53M320-16,6G基站晶振